硅基星轨

一、TPU基础概念

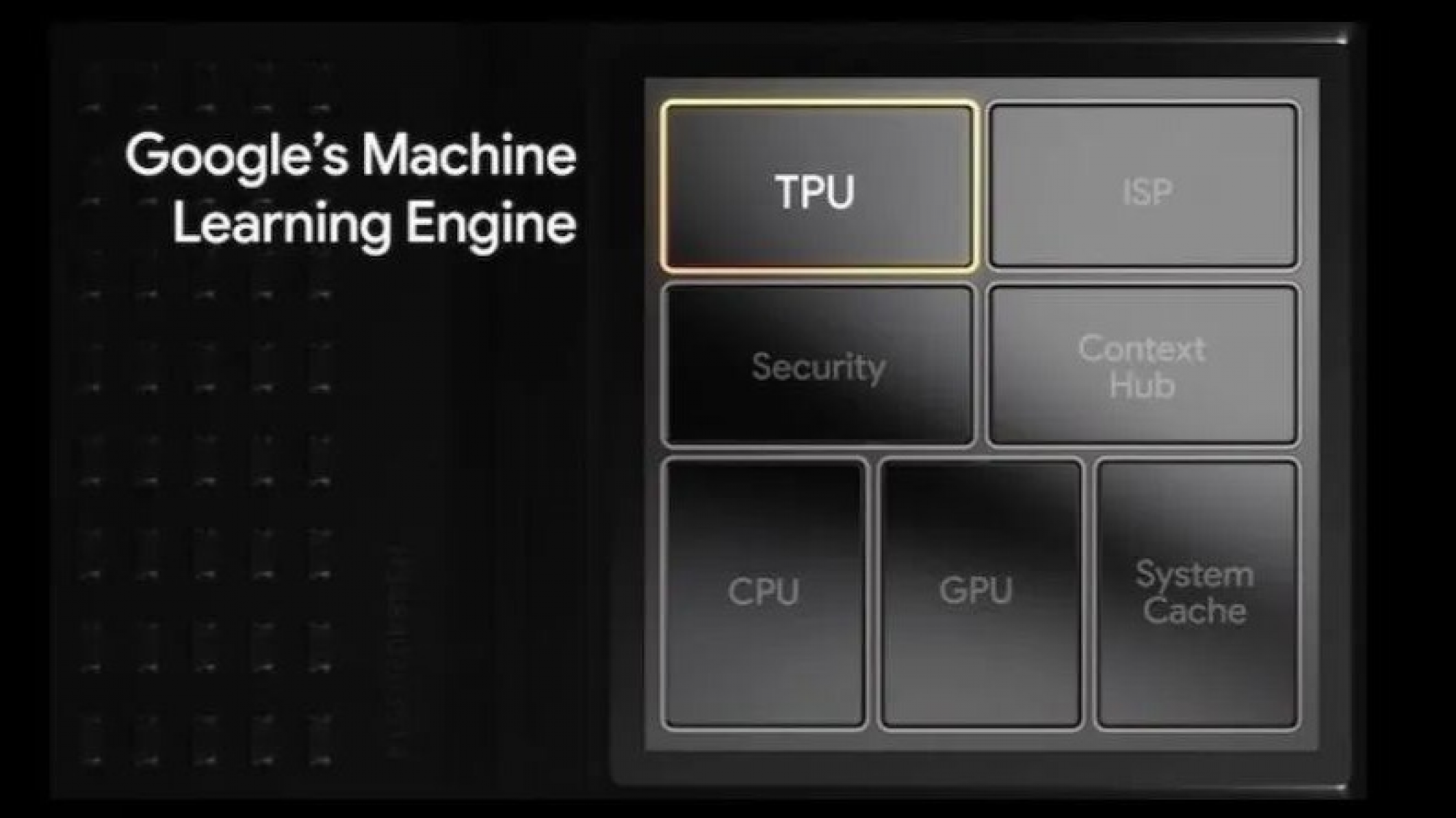

1.定义:张量处理单元(Tensor Processing Unit,TPU)是谷歌公司专为加速机器学习任务而设计的专用集成电路(ASIC),旨在高效处理矩阵运算和张量操作,满足深度学习算法对大量数据并行计算的需求 。

2.诞生背景:随着深度学习算法的发展,传统CPU和GPU在处理大规模神经网络计算时面临效率瓶颈,谷歌为提升自身AI应用(如语音识别、图像搜索等)的计算性能,研发出TPU以应对日益增长的计算需求 。

3.发展历程:2015年第一代TPU诞生,专为推理设计;历经多次迭代,到2023年第七代TPU(Ironwood)发布,性能实现大幅跃升,从服务早期AI应用到如今支持超大规模模型训练 。

4.与通用处理器区别:通用处理器(如CPU)擅长逻辑控制和通用计算任务,具有通用性强但计算效率相对较低;GPU适合并行计算,在图形处理和科学计算等方面表现出色,但在深度学习特定计算模式下并非最优;TPU则针对深度学习中的矩阵乘法、卷积等核心运算进行深度优化,在这些任务上具有更高的计算效率和能效比 。

5.地位:在人工智能计算领域,TPU是推动深度学习发展的关键力量,为大规模模型训练和推理提供强大算力支持,助力谷歌在AI领域保持技术领先 。

6.设计理念:围绕深度学习算法特点,采用脉动阵列(Systolic Array)等架构,优化矩阵计算,减少数据搬运,提升计算效率和能效 。

7.架构组成:通常包含计算核心(如多个矩阵乘法单元)、缓存、内存控制器、通信接口等组件。

8.计算核心作用:负责执行张量运算,是TPU实现高效计算的关键部分 。

9.缓存功能:存储临时数据,减少对外部内存的访问,提高数据读取速度。

10.内存控制器职责:管理内存访问,协调数据在内存与计算核心之间的传输。

11.通信接口类型及作用:如PCIe接口用于与主机通信,实现数据交互;片间通信接口用于多个TPU芯片间互联,构建大规模计算集群 。

12.硬件实现方式:通过专用集成电路设计,采用先进制程工艺(如从早期的28nm到后来的更先进制程)制造 。

13.物理形态:常见为芯片形式,可集成在服务器主板或专用加速卡上。

14.封装类型:如BGA(球栅阵列)封装,以满足芯片电气连接和散热需求 。

15.在数据中心的部署方式:可通过PCIe插槽插在服务器主板上,也可集成在专门的TPU板卡中,多个TPU板卡组成TPU集群,部署在数据中心机柜 。

16.与其他硬件设备的协同工作:与CPU协同,CPU负责任务调度和逻辑控制,TPU专注深度学习计算;与内存协同,快速读写数据;与网络设备协同,实现数据的高速传输 。

17.软件支持体系:依赖谷歌自研的TensorFlow等深度学习框架,通过特定的API和驱动程序实现对TPU的调用和管理 。

18.驱动程序功能:实现TPU硬件与操作系统之间的通信,管理TPU资源 。

19.编程语言支持:支持Python等常用编程语言,方便开发者使用 。

20.应用开发流程:包括模型设计、代码编写(基于深度学习框架调用TPU)、模型训练或推理、性能优化等环节 。

二、TPU产品代次

21.第一代TPU(2015年):专为推理设计,峰值算力92 TFLOPS(FP16) ,采用28nm工艺制造,频率为700MHz,热设计功耗为40瓦 。具有28MiB的芯片内存和4MiB 32位累加器,用于存储256x256系统阵列的8位乘法器的结果 。主要针对早期神经网络(如CNN、RNN、LSTM,主要优化前两者推理场景)进行优化 。

22.第二代TPU(2017年):支持训练和推理,引入了脉动阵列架构,提升计算效率。开始支持谷歌的分布式训练框架,可多个芯片组成TPU Pod集群 ,在性能和扩展性上有显著提升 。

23.第三代TPU(2018年):算力达到100 TFLOPS(FP32) ,内存带宽进一步提升,首次引入分布式训练框架 ,可用于更大规模模型训练,在训练和推理性能上都有较大进步 。

24.第四代TPU(2020年):性能持续增强,在制程工艺、芯片架构等方面优化,采用新的互联技术提升芯片间通信速度,进一步提升了集群计算能力。

25.第五代TPU(未公开详细信息推测):在性能、能效比等方面可能有新突破,可能采用更先进制程,优化芯片架构,提升内存带宽和计算核心性能。

26.第六代TPU(2021年):算力达到1 PFLOPS(FP32) ,内存带宽3 TB/s,支持3D堆叠封装和液冷技术 ,用于训练千亿参数模型 ,在大规模模型训练上具备更强实力 。

27.第七代TPU(2023年,代号Ironwood):性能较第六代提升10倍,单芯片算力达到1 exaFLOP(FP8精度) 。通过混合键合将逻辑层与内存层以10微米间距堆叠,内存带宽提升至12 TB/s,功耗降低30% 。每个FlexCore包含4096个MAC,支持多种混合精度 。采用硅光子集成和波分复用技术,芯片间通信带宽每秒10 TB/s,通信延迟5微秒 。

28.历代TPU制程工艺变化:从28nm开始,随着技术发展逐渐采用更先进制程,制程越小,芯片集成度越高,性能越强,功耗越低 。

29.芯片大小变化趋势:随着集成度提升和架构优化,芯片大小可能在保证性能前提下趋于合理,不一定单纯增大或减小。

30.内存容量提升情况:从第一代到第七代,内存容量不断增大,如第七代TPU内存带宽达12 TB/s,是第六代的4倍,满足大规模数据存储和快速访问需求 。

31.时钟速度演进:时钟速度逐步提升,以提高计算核心的运算频率,加快数据处理速度。

32.热设计功耗变化:早期功耗相对较低,如第一代40瓦,随着性能提升,功耗有所增加,第七代单芯片约400 - 500W,但通过技术优化(如架构、散热设计),集群能效比提升50% 。

33.各代TPU适用场景差异:早期主要用于推理和小规模模型训练,随着性能提升,中晚期可用于超大规模模型训练、科学计算加速等复杂场景。

34.第一代TPU技术优势:在早期为深度学习推理提供了专门优化的硬件加速,相比通用处理器在推理任务上有显著效率提升。

35.第二代TPU技术创新点:引入脉动阵列架构,实现高效矩阵计算,支持分布式训练框架,开启大规模集群计算能力。

36.第三代TPU对模型训练的影响:使更大规模模型训练成为可能,提升训练速度和效率,推动深度学习模型规模和复杂度发展。

37.第四代TPU在互联技术上的改进:采用新互联技术,提升芯片间通信速度,减少数据传输延迟,增强集群计算性能。

38.第五代TPU可能的突破方向推测:可能在异构计算集成、量子计算协同等前沿领域探索,进一步提升性能和拓展应用范围。

39.第六代TPU采用3D堆叠封装和液冷技术的意义:3D堆叠封装增加芯片集成度和内存带宽,液冷技术解决高功耗散热问题,保障芯片稳定运行 。

40.第七代TPU的架构革命体现在哪些方面:包括混合键合内存堆叠、计算单元优化、缓存机制升级、稀疏计算加速器应用、硅光子集成等多方面架构革新。

三、TPU核心参数

41.算力:衡量TPU计算能力指标,如第七代TPU单芯片算力1 exaFLOP(FP8精度) ,算力越高,单位时间内可完成的计算任务越多 。

42.精度:支持的数据精度,如FP32、FP16、BF16、FP8、INT8等 ,不同精度适用于不同计算场景,低精度在保证一定准确性下可提升计算效率 。

43.内存带宽:数据在内存与计算核心之间传输速度,如第七代TPU内存带宽12 TB/s ,高带宽可减少数据等待时间,提升计算效率 。

44.芯片间通信带宽:多个TPU芯片间通信速度,第七代TPU芯片间通信带宽每秒10 TB/s ,影响集群计算性能 。

45.通信延迟:芯片间通信数据传输延迟,第七代TPU芯片间通信延迟5微秒 ,延迟越低,集群协同计算效率越高 。

46.缓存容量:各级缓存大小,如第七代TPU L3缓存容量达64MB/核心 ,缓存越大,可存储更多临时数据,减少对外部内存访问 。

47.缓存命中率:数据请求能在缓存中找到的概率,命中率越高,数据读取速度越快,计算效率越高。

48.功耗:TPU运行消耗功率,第七代TPU单芯片约400 - 500W ,功耗影响散热和运行成本 。

49.能效比:单位功耗下计算能力,第七代TPU集群能效比(TOPS/W)提升50% ,能效比越高,能源利用效率越高 。

50.工作频率:计算核心运行频率,影响数据处理速度。

51.逻辑门数量:反映芯片复杂度和计算能力,逻辑门数量越多,可实现更复杂计算功能。

52.制程工艺:如28nm、更先进制程等,制程越小,芯片性能和集成度越高 。

53.可靠性指标:如平均故障间隔时间(MTBF) ,衡量TPU稳定运行能力 。

54.抗干扰能力:抵抗外部电磁干扰等能力,保障TPU在复杂环境稳定工作 。

55.可扩展性:能否方便增加TPU数量构建更大规模集群,提升计算能力 。

56.兼容性:与其他硬件设备(如服务器、网络设备)和软件(深度学习框架)兼容程度。

57.数据吞吐量:单位时间内TPU处理数据量,体现数据处理能力 。

58.并行计算能力:支持并行计算任务数量和效率,TPU通过多个计算核心实现强大并行计算能力 。

59.任务处理延迟:从接收任务到完成任务总时间,延迟越低,实时性越好。

60.资源利用率:TPU硬件资源实际使用比例,利用率越高,资源浪费越少 。

四、TPU关键技术

61.脉动阵列(Systolic Array)架构:一种高效矩阵计算架构,数据像血液流经心脏一样在计算单元中流动,减少数据搬运,提高计算效率。

62.低精度计算技术:通过量化技术将数据精度降低(如从FP32到INT8) ,在推理场景可在保持一定精度下提升计算速度和降低资源消耗 。

63.稀疏计算技术:利用神经网络中大量零值数据特点,通过动态稀疏化技术自动屏蔽零值数据,减少计算量,提升计算效率。

64.3D堆叠封装技术:将多个芯片或芯片层堆叠在一起,增加芯片集成度和内存带宽,缩短数据传输距离。

65.液冷技术:用于解决高功耗芯片散热问题,如第七代TPU采用液冷技术保障稳定运行 。

66.硅光子集成技术:在芯片上集成激光器和光调制器,利用光信号传输数据,减少传统电缆延迟,提升通信速度。

67.波分复用(WDM)技术:通过不同波长光信号并行传输,增加通信链路带宽,如第七代TPU单链路带宽达1.6 TB/s 。

68.自动并行化技术:自动将计算任务分解为多个并行子任务,充分利用TPU并行计算资源 。

69.混合精度自动转换技术:根据计算需求自动在不同精度间转换,平衡计算精度和效率。

70.Mesh TensorFlow优化技术:针对TPU优化的分布式计算框架,支持大规模模型分布式训练 。

71.内存优化管理技术:合理分配和管理内存资源,提高内存使用效率。

72.缓存优化技术:优化缓存结构和算法,提高缓存命中率,减少内存访问。

73.指令集优化:专门为深度学习计算设计指令集,提高指令执行效率。

74.数据预取技术:提前将数据从内存读取到缓存,减少计算等待时间。

75.流水线技术:将计算任务分解为多个阶段,各阶段并行执行,提高整体计算速度。

76.容错技术:在硬件出现故障时,保证计算任务正确执行或快速恢复。

77.负载均衡技术:在多个计算核心或TPU芯片间均衡分配计算任务,提高资源利用率 。

78.动态电压频率调整(DVFS)技术:根据计算负载动态调整TPU电压和频率,降低功耗 。

79.时钟管理技术:精确管理时钟信号,保证各组件同步工作。

80.硬件虚拟化技术:允许多个虚拟机或任务共享TPU硬件资源 。

五、TPU关键友商

81.英伟达(NVIDIA):GPU领域巨头,在AI计算芯片市场竞争力强。产品如A100基于安培架构,性能强大,20倍于前一代,引入tf - 32格式,有高GPU - to - GPU带宽 。优势在于成熟软件生态和广泛应用,挑战是需升级软件栈 。

82.AMD:推出Radeon Instinct MI250x GPU,用于高性能计算(HPC) ,在FP64计算中有巨大吞吐量和性能 。优势是软件栈不断改进,可兼顾AI和HPC,挑战是对AI计算专注度弱 。

83.英特尔(Intel):凭借CPU技术基础和在数据中心领域积累,开发AI计算芯片。虽在AI加速芯片市场份额暂不高,但技术实力和市场渠道强 。优势是技术研发能力和生态系统,挑战是追赶专业AI芯片厂商进度 。

84.华为(昇腾系列):昇腾芯片针对AI计算,采用达芬奇架构,有高算力和低功耗特点 。优势是适应多种AI场景,构建全栈AI解决方案,挑战是面临外部限制 。

85.寒武纪:专注AI芯片研发,思元系列芯片在智能安防、云计算等领域应用 。优势是针对AI算法深度优化,产品迭代快,挑战是市场竞争和生态建设 。

86.地平线:聚焦边缘AI芯片,征程系列芯片在自动驾驶等边缘场景有应用 。优势是对边缘场景理解深,产品适配边缘计算需求,挑战是拓展市场和提升性能 。

87.燧原科技:产品如邃思芯片面向云端AI训练,有高算力和性价比 。优势是自主研发架构和技术创新,挑战是在竞争中扩大市场份额 。

88.友商产品性能对比维度:算力、精度支持、内存带宽、芯片间通信能力、功耗、能效比。

89.友商产品价格策略:根据性能、市场定位和竞争情况制定,高性能产品价格高,面向大众市场产品注重性价比。

90.友商产品生态建设情况:英伟达有完善CUDA生态;华为构建昇腾AI生态;寒武纪、地平线等也在积极构建开发者社区和生态 。

91.市场竞争格局分析:英伟达占据较大市场份额,TPU凭借独特技术和谷歌应用优势有一席之地,其他厂商在不同细分领域竞争 。

92.未来竞争趋势预测:技术竞争更激烈,向边缘计算、物联网等领域拓展,异构计算和芯片融合成趋势。

93.TPU与友商产品在不同应用场景的适应性:TPU在谷歌内部大规模AI模型训练和推理优势大;英伟达产品在通用AI计算和游戏等领域广泛应用;华为昇腾适应多种AI场景;地平线芯片适合边缘自动驾驶 。

94.友商在技术研发方面的投入和方向:持续投入研发,方向包括提升算力、降低功耗、优化架构、拓展应用场景。

95.新进入者的机会与挑战:机会是新兴应用场景和技术创新点,挑战是技术积累、市场竞争和生态建设。

96.谷歌如何保持TPU在市场中的竞争力:持续技术创新,优化性能和能效;拓展应用场景;完善软件生态。

97.友商之间的技术合作与竞争关系:既有竞争,也在部分技术(如异构计算)和标准制定上有合作。

98.TPU面临的市场竞争压力来源:来自英伟达等成熟AI

99.TPU面临的市场竞争压力来源:来自英伟达等成熟AI芯片厂商的技术迭代与生态优势,AMD在高性能计算与AI融合领域的持续发力,以及国内厂商凭借本土市场与政策支持的快速崛起,都对TPU的市场份额与技术领先地位形成挑战。

100.TPU与友商在芯片架构设计上的差异:TPU采用脉动阵列架构,以数据流驱动计算,高度适配深度学习的矩阵运算;英伟达GPU采用SIMT(单指令多线程)架构,在通用并行计算上更具灵活性;华为昇腾芯片的达芬奇架构则通过3D Cube计算引擎实现高效张量计算,架构设计的不同导致其在不同应用场景中展现出差异化优势。

101.未来TPU及友商产品的发展趋势:技术上,将向更高算力、更低功耗、支持更复杂算法方向发展;架构上,异构融合成为主流,集成CPU、GPU、AI加速器等多种计算单元;应用领域不断拓展,从云端AI计算延伸至边缘计算、量子计算等新兴场景;生态建设方面,各厂商将通过开源社区、开发者支持计划等方式,构建更完善的软件生态系统,增强产品竞争力。

六、TPU的应用生态

102.谷歌内部应用场景:在谷歌搜索引擎中,TPU加速语义理解与搜索结果排序,提升搜索精准度与响应速度;谷歌翻译借助TPU实现实时多语言翻译,支持海量语言模型的高效运行;在谷歌相册的图像识别与分类、YouTube视频推荐算法等服务中,TPU也发挥着核心算力支撑作用 。

103.开放云服务应用:通过Google Cloud AI Platform,TPU以云服务形式向外部开发者与企业开放。例如,科研机构利用TPU集群训练复杂的生物医学模型,加速药物研发进程;金融机构使用TPU进行高频交易策略的训练与实时风险评估;互联网企业借助TPU优化广告推荐系统,提高广告投放效率与用户体验 。

104.开源框架支持:谷歌通过开源TensorFlow框架,深度整合TPU支持。TensorFlow的XLA编译器可针对TPU进行代码优化,将高级语言编写的深度学习模型自动转换为高效的TPU可执行代码;同时,提供TPU - specific的API接口,方便开发者调用TPU资源,极大降低了TPU的使用门槛 。

105.开发者社区建设:谷歌积极构建TPU开发者社区,定期举办线上线下技术交流活动、黑客马拉松等,分享TPU技术经验与最佳实践;发布TPU案例库与技术文档,鼓励开发者贡献开源项目,形成技术共享、共同进步的生态环境 。

106.行业合作生态:与汽车制造商合作,探索TPU在自动驾驶领域的应用,如训练高精度的感知与决策模型;与医疗设备企业联合,开发基于TPU的医学影像分析系统,辅助疾病诊断;与高校、科研院所建立合作关系,支持学术研究与人才培养,推动AI技术创新 。

七、TPU技术发展的挑战与对策

107.硬件设计挑战:随着计算需求的不断增长,TPU面临更高的算力密度与散热平衡难题。在追求极致算力的同时,芯片内部集成度不断提高,产生的热量大幅增加,传统散热技术难以满足需求 。

108.硬件应对策略:持续优化芯片架构设计,采用更先进的制程工艺降低功耗;探索新型散热材料与散热方式,如纳米流体散热、微通道散热等;通过3D堆叠技术,在提高集成度的同时优化散热路径 。

109.软件适配挑战:深度学习算法快速迭代,新的模型结构与计算模式不断涌现,TPU需要及时适配以保持高效运行;同时,不同开发者使用的深度学习框架与编程习惯存在差异,增加了软件适配的复杂性 。

110.软件应对策略:加强与开源社区合作,及时跟踪算法发展趋势,更新TPU软件支持库;开发更智能的自动适配工具,实现对不同算法与框架的动态优化;提供丰富的示例代码与开发指南,帮助开发者快速掌握TPU编程技巧 。

111.生态竞争挑战:AI芯片市场竞争激烈,英伟达CUDA生态、华为昇腾生态等不断完善,吸引大量开发者与企业用户,TPU需要进一步扩大生态影响力,吸引更多外部资源 。

112.生态应对策略:加大生态建设投入,推出更多优惠政策与激励措施,吸引开发者与企业加入TPU生态;加强与第三方软件开发商合作,丰富TPU应用场景;积极参与行业标准制定,提升TPU在行业内的话语权 。

113.成本控制挑战:先进制程工艺的采用、复杂架构设计以及大规模集群建设,导致TPU研发与生产成本居高不下,限制了其在部分对成本敏感领域的应用 。

114.成本应对策略:通过规模化生产降造成本;优化设计方案,在保证性能的前提下简化架构;探索与其他企业的联合研发模式,分摊研发成本。

115.数据安全挑战:在AI计算过程中,TPU处理大量敏感数据,如用户隐私信息、企业核心数据等,面临数据泄露、恶意攻击等安全风险 。

116.安全应对策略:在硬件层面,集成加密模块,实现数据的端到端加密;在软件层面,加强访问控制与权限管理,采用安全沙箱技术隔离计算任务;建立完善的安全审计机制,实时监控数据操作行为。

八、TPU与行业标准

117.AI芯片性能评估标准:参与制定行业通用的AI芯片性能评估指标,如INT8/FP16/FP32算力、能效比、数据吞吐量、模型训练与推理延迟等,为用户选择芯片提供客观依据 。

118.软件接口标准:推动AI芯片软件接口的标准化进程,促进不同芯片与深度学习框架之间的兼容性,降低开发者的适配成本,提高开发效率 。

119.能耗标准:积极响应绿色计算理念,参与制定AI芯片能耗标准,引导行业向低功耗、高能效方向发展 。

120.数据安全与隐私保护标准:联合行业组织,制定AI芯片数据安全与隐私保护标准,规范数据采集、存储、处理与传输等环节的安全要求 。

121.芯片可靠性标准:制定AI芯片可靠性评估标准,包括平均故障间隔时间(MTBF)、环境适应性、抗干扰能力等指标,确保芯片在不同应用场景下的稳定运行。